# EmbeddedSystems

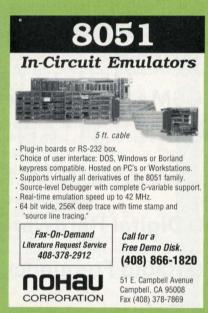

# Cut Development Time

**Using In-Circuit Emulators and BDM's**

### **Macros**

- · Macro debug capability

- Project support

- · Command line

- Shadow RAM support

- · Single step in your macro

- · GUI capable macros

### **Key Features**

- Real-time emulation at maximum chip speeds

- High level support for popular C compilers

- · Advanced tracing capabilities

- Configurable user interface with remote hookup capability

- High speed connection to PC through parallel port (LPTx) or plug-in ISA card

Nohau Supports These Microcontroller Families 8051 80C196 683xx 68HC11 P51XA ST10 MCS296 MCS251 68HC16 C166 68HC12 M16C

# www.nohau.com

51 East Campbell Avenue, Campbell, CA 95008 Phone: 1-888-88NOHAU (1-888-886-6428) Fax: 408-378-7869 E-mail: sales@nohau.com

visionICE

visionCLICK

visionPROBE

**Embedded Support Tools Corporation**

**EmbeddedSystems**

# contents

APRIL 2000

### **COVER**

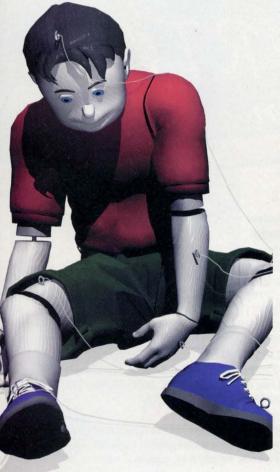

Managing people, processes, and technology may require pulling a few strings.

Cover illustration by Rupert Adley.

### **Cover Story**

### Manage Your Embedded Project As the embedded systems development effort shifts more

As the embedded systems development effort shifts more toward software and schedules begin to slip, project management becomes key to increasing productivity.

BY SCOTT BRIGGS

### Part 2 in a Series

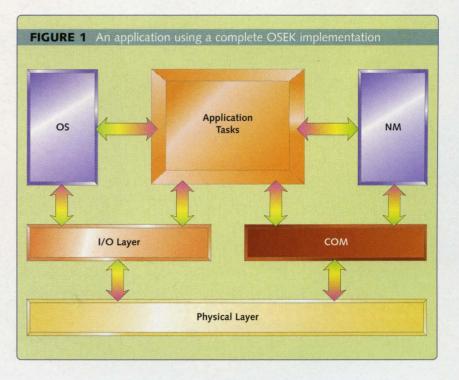

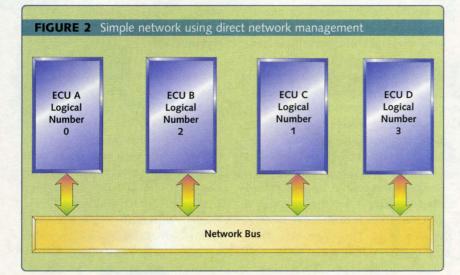

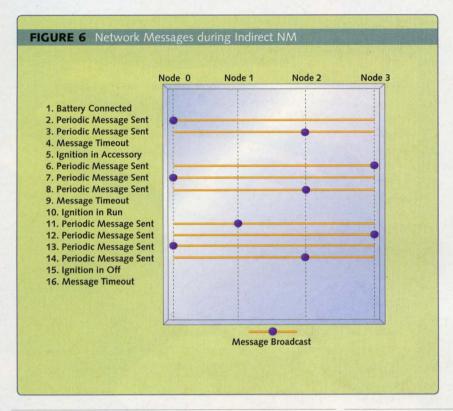

### OSEK/VDX Network Manager and Implementation Language

The OSEK specification covers three subsystems commonly found in automotive applications: operating systems, communications, and network management. This article completes a discussion of all three.

BY JOSEPH LEMIEUX

96

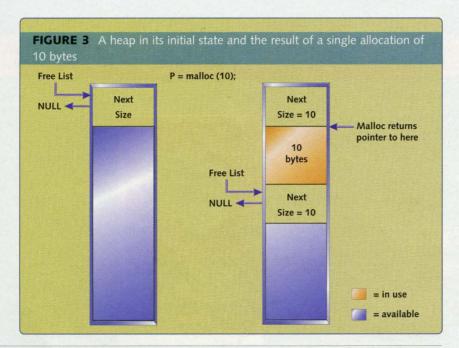

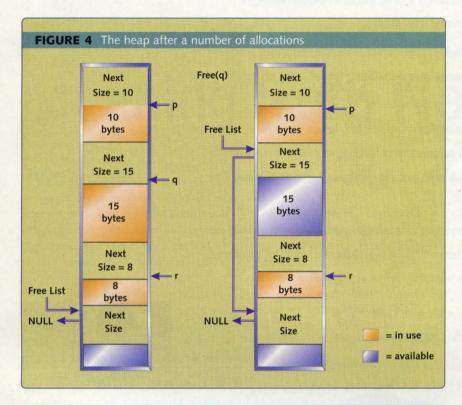

### Safe Memory Utilization

Whether you're using only static memory, a simple stack, or dynamic allocation on a heap, you've got to proceed cautiously. Embedded programmers cannot afford to ignore the risks inherent in memory utilization.

BY NIALL MURPHY

85

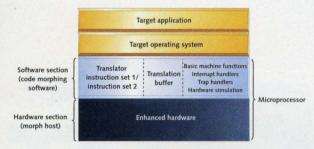

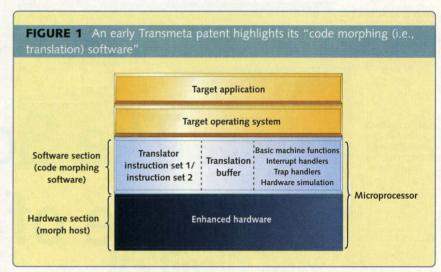

An early look into Transmeta's Crusoe processor and its "code morphing" capabilities.

### **Featured Section**

# internet appliance design

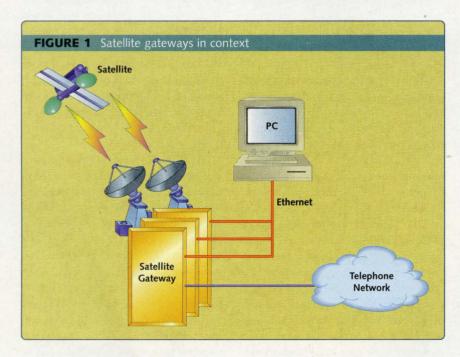

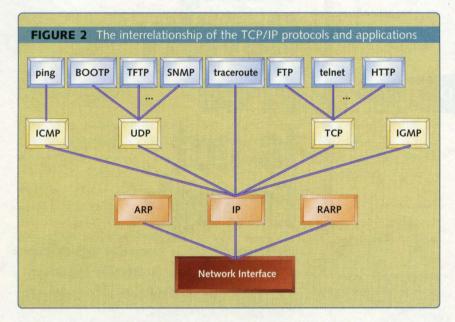

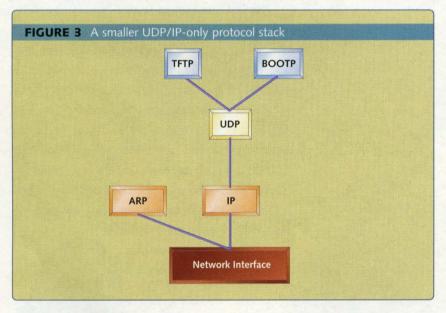

### 49 CONNECTING... TCP/IP or Not TCP/IP?

The question is not simply whether or not to use TCP/IP for your internet appliance, but which subset of the networking protocols is right for your project.

BY MICHAEL BARR

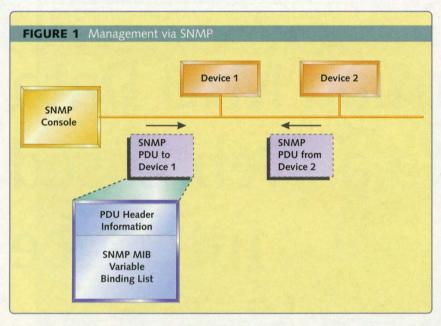

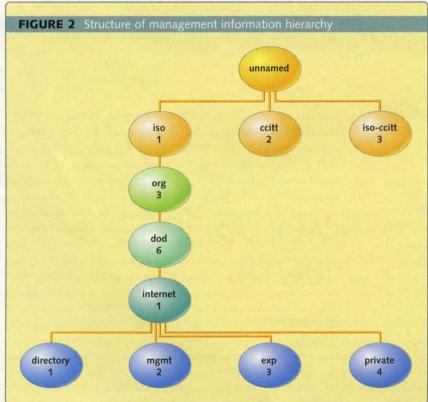

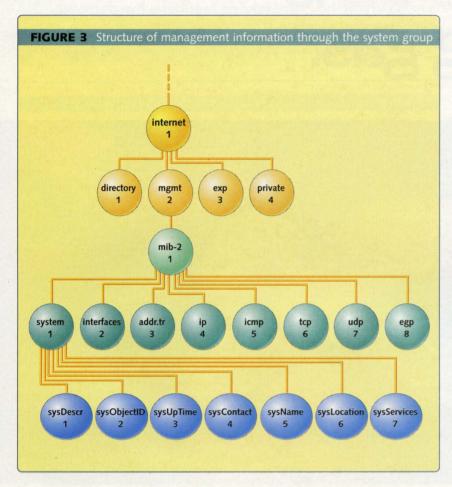

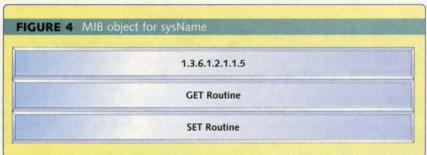

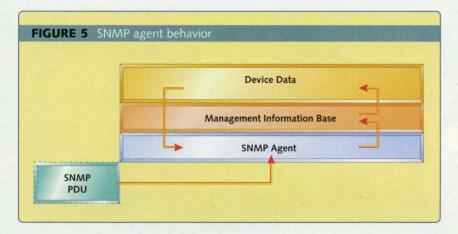

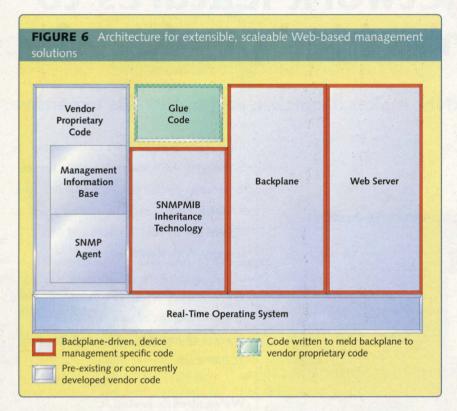

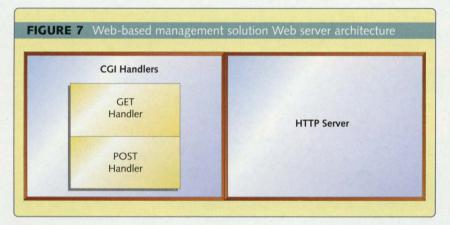

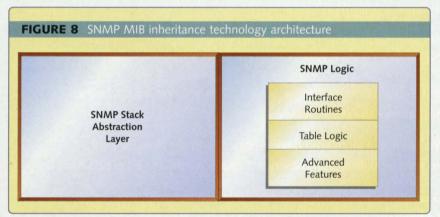

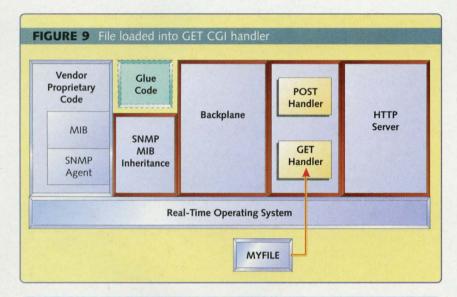

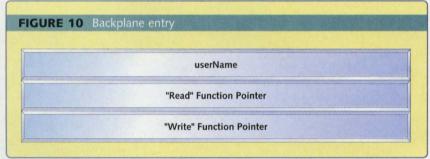

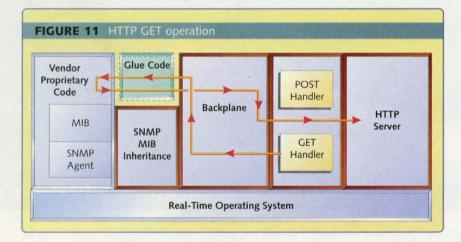

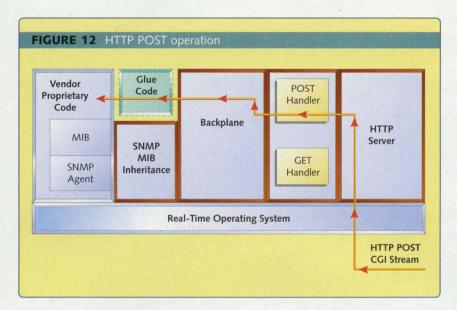

### **55** Exposing MIB Data to a Web-based Interface

Web-based management is essential these days. With the right architecture and an SNMP MIB inheritance library, legacy management code can remain untouched, and you can realize tremendous design and product life cycle benefits.

BY KEDRON WOLCOTT

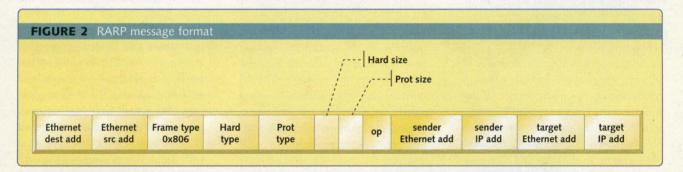

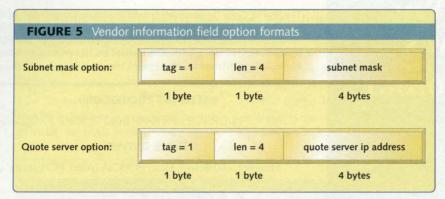

### **71** Configuring TCP/IP Hosts, Methods, and Protocols

Every TCP/IP enabled device needs to be configured. Of course, there are several valid ways to go about it. This article will help you select the best configuration technique for your system.

BY CHRISTOPHER D. LEIDIGH

### **New Technology**

### **85** The Software Side of Crusoe

With considerable ballyhoo, Transmeta has finally introduced its new processor family. Here's a take on what it will mean to software developers.

BY ALEXANDER WOLFE

89 Embedded Internet Tools

New internet appliance design products.

128

Microchip's PIC16F87X family of flash chips.

### departments

5 #INCLUDE

Vehicular Rant

BY LINDSEY VEREEN

**7 NEWS VECTORS**

127 NEW PRODUCT GALLERY

**131 RECRUITMENT**

**132 MARKETPLACE**

136 ADVERTISER INDEX

### columns

11 PROGRAMMER'S TOOLBOX

A Simulator's Paradise

BY JACK W. CRENSHAW

91 PROGRAMMING POINTERS

Passing Parameters by Value with const

BY DAN SAKS

121 SPECTRA

Meaning from Noise

BY DON MORGAN

137 BREAK POINTS

In Praise of Kids These Days

BY JACK G. GANSSLE

141 STATE OF THE ART

Great Reckoning, Little Room

BY P.J. PLAUGER

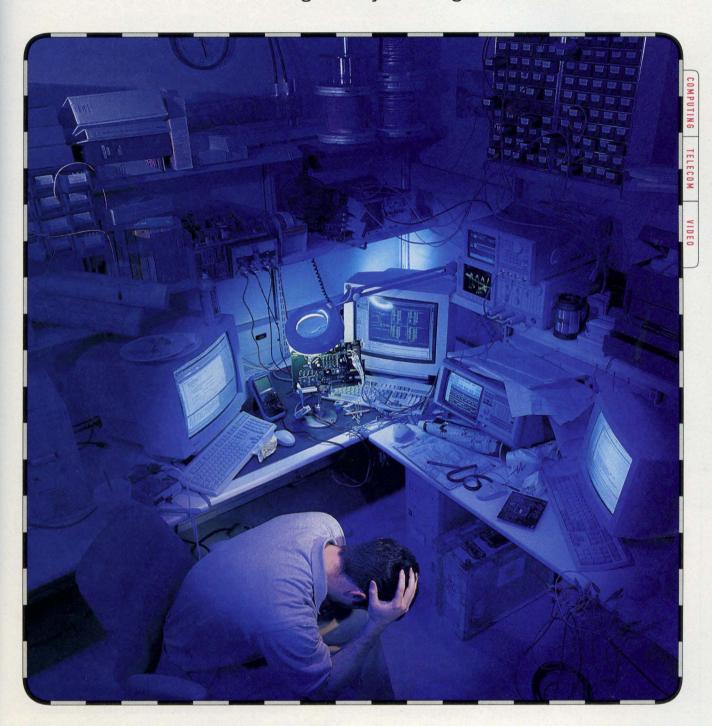

# "If only I had spent less time on debug

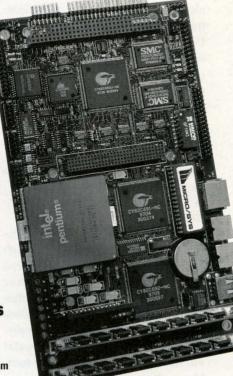

If you are developing a Pentium

class target using a reference

design or off-the-shelf board,

please take a moment to speak

with our staff. They will insure your

design is on track, and tool friendly

if debug is needed in the future.

I remember when I budgeted for my project. I refused to spend money on debug tools. I didn't think I would need them. The money I saved would make me a hero.

Now, my project is one month, two months ... six months overdue. Nobody thinks I'm a hero. What would I give to get some of that time back?

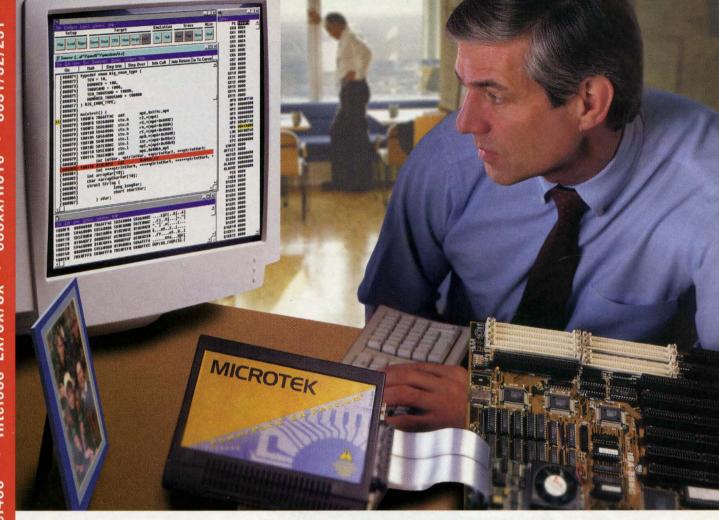

Microtek debug tools can make time. They speed up development and testing, saving you precious time at the end of the project, where you need it most!

Microtek emulators offer the debug features you need to track down and correct software, hardware, and system integration issues. They can find the errors software debuggers cannot see.

First, emulators can debug before the operating system is functioning. If an unexpected issue is affecting boot up, an emulator can find it. They are also operational after a hard crash. This is significant, because software debuggers lose debug information. Microtek emulators keep track of the last 128 KB of bus cycles, allowing you to sift through and find the problem.

Additional interfaces: CAD/UL® and Windriver Tornado II®

Finally, if there is a subtle issue during the integration of hardware, Microtek EA emulators are capable of providing a clock-cycle-byclock-cycle trace that allows you to view each signal and determine whether it was in the correct state. Microtek's tools are clearly

superior to software debug solutions.

There has never been a project that couldn't use more time when it's critical ... like in final testing when everything has come together ... or in final debug, when everything is going down in flames.

Wouldn't it be great to deliver your next project on time? Next time, be sure to put a Microtek emulator in your project plan from the start.

It will help take the knot out of your stomach. And it will improve your company's bottom line!

# MICROTEK IN-CIRCUIT EMULATORS

1 (800) 886-7333

Phone (503) 533-4463 Fax (503) 533-0956 Email - info@microtekintl.com

## Vehicular Rant

Maybe I'm just getting old, but I don't get the concept of the sports utility vehicle. How can a cross between a pickup truck and a station wagon be the coolest thing on wheels for the smart set? Among their myriad features, SUVs are hard to park, expensive to insure, and gas guzzlers.

In San Francisco, a city of narrow streets and few parking places, SUVs have become as common as pigeons, and nearly as much of a nuisance. Because of their size, they take up a disproportionate amount of precious parking space. Each morning you can find dozens of them perched on sidewalks because there were no spaces large enough the night before. Now you'd think that the rationale for people to buy SUVs would be to go skiing in the Sierras. But no, many owners don't want to besmirch their vehicles with mud and snow.

Now I'm not trying to annoy all of you SUV drivers out there. I certainly recognize the value of four-wheel drive for people living in snowy climes. And I like the way you can sit high enough to see over traffic, such as other SUVs. My beefs are twofold. First is the disparity between the large SUVs and small compacts. I'd like to feel that if I were driving a Geo Metro, I'd have a shot at surviving a collision with another vehicle.

My other beef is about the fuel economy and emissions that characterize these vehicles. That problem appears to be going away-eventually-thanks to recently passed legislation. From then on it's up to the auto industry to squeeze out all the gas mileage and extra weight.

If we were to eliminate one or the other, small fuel-efficient vehicles don't seem the ones to put on the chopping block. I guess mine is a minority viewpoint. SUVs aren't disappearing from the streets and highways of America. And to make matters worse, I'm even seeing more Hummers on the streets of San Francisco. Figure that one out. Fortunately we have the technology to help make other (smaller) vehicles safer to the occupants when SUVs try to occupy the same space at the same time.

We're all aware of the litany of virtues that embedded intelligence can add to products: features, reliability, reduced power consumption, and added safety. Those virtues are being exploited more and more by the auto industry. High-end automobiles now boast more than 60 processors. The auto industry is beginning to depend on embedded systems, as was clear by the number of automotive electronics engineers in attendance at last month's embedded systems conference in Chicago. The use of embedded systems has made automobiles safer and better performing than before CAFE (corporate average fuel economy) standards were put into place in the 1970s.

Since SUVs are not going away, and their drawbacks (other than size) can only be mitigated through technology, we can take comfort in one additional virtue that embedded systems offer. In a small way they can help save us from ourselves.

lvereen@cmp.com

### EDITORIAL DIRECTOR

Lindsey Vereen, lyereen@cmp.com

### MANAGING EDITOR

Felisa Yang, fyang@cmp.com

### TECHNICAL EDITOR

### SENIOR SPECIAL PROJECTS EDITOR

### CONSULTING TECHNICAL EDITORS

Jerome L. Krasner, PhD

### CONTRIBUTING EDITORS

Jack W. Cren Larry Mittag

### VICE PRESIDENT/ELECTRONICS

EMBEDDED/DSP GROUP DIRECTOR

Eric Berg, (415) 278-5220

### CALIFORNIA SALES MANAGER

### CALIFORNIA SALES ASSISTANT

WESTERN ACCOUNT EXECUTIVE

### EASTERN REGIONAL SALES MANAGER

EASTERN SALES

PRODUCTION COORDINATOR

### CIRCULATION MANAGER

### CIRCULATION DIRECTOR

### SUBSCRIPTION CUSTOMER SERVICE

Toll free: (877) (847) 291-5215

# (847) 291-3215 exp®omeda.com Back issues may be purchased on a prepaid basis through: Miller Freeman, 1601 West 23rd St., Suite 200, Lawrence, KS 66046; (800) 444-4881; (785) 841-1631

Sherry Bloom, (415) 808-3980

### ONLINE PRODUCTION COORDINATOR

PRESIDENT/CEO, CMP MEDIA INC.

### EXECUTIVE VICE PRESIDENTS

Regina Starr Ridley John Russell Steve Weitzner Tony Uphoff

### SENIOR VICE PRESIDENT/ GLOBAL SALES & MARKETING Bill Howard

SENIOR VICE PRESIDENT/ BUSINESS DEVELOPMENT

PRESIDENT/ELECTRONICS

Visit our Web site at www.embedded.com

#

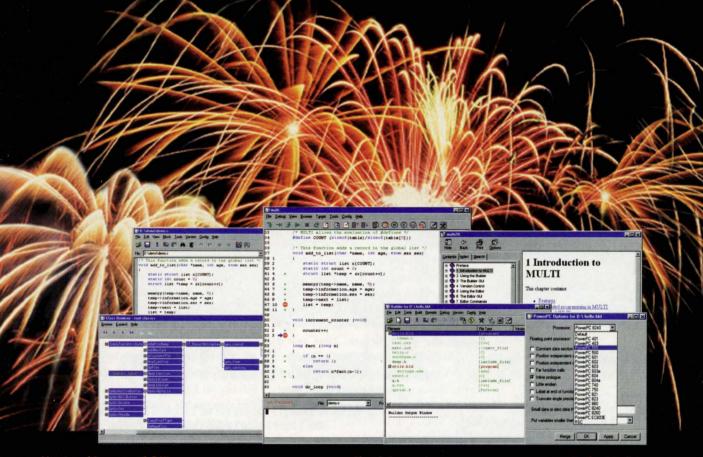

The New IDE for the New Millennium

- · New and Improved GUI

- · Graphical Browser

- · On-Line Help

- · Syntax Coloring and Auto Indenting

- Simulator

- Version Control

- · C++ Debugging

- EventAnalyzer

- · Project Builder

- · Code Coverage

- · Run-Time Error Checking

- · Profiling

The Best Compilers.

The Best Debuggers.

Now, all wrapped up in a brand new, powerful, easy to use IDE. Once you try MULTI 2000, you won't want to struggle with "old fashioned" tools ever again. Contact us now for a start the millennium

Free Evaluation CD and

start the millennium with a bang!

Tel: 805.965.6044 • Fax: 805.965.6343 • Email: sales@ghs.com • www.ghs.com Copyright ©1999 Green Hills Software, Inc. MULTI is a registered trademark of Green Hills Software, Inc.

### **QED launches IPO**

Quantum Effect Devices Inc. announced the initial public offering on February 1 of its common stock trading under the symbol "QEDI" on NASDAQ. In its first day of trading, the stock opened at 39 1/4 and closed at 56 1/2. At press time, the stock was at 95 3/16.

The initial public offering price for the 3,720,000 shares of common stock was \$16 per share. The company offered 3 million shares and a shareholder offered the remaining 720,000. The offering was managed by Morgan Stanley Dean Witter, Lehman Brothers, and Robertson Stephens.

Quantum Effect Devices, headquartered in Cambridge, MA, was founded in 1991 and develops embedded microprocessors for use in information processing in networking/communications infrastructure equipment.

### **Briefly Noteds...**

Wind River Systems will resell Rapid Logic's MIBway for Wind Web Server product through its Wind River Direct program, MIBway provides support for Wind River's Tornado platform and VxWorks. \* and **FSMLabs** Synergy Microsystems have released the beta version of RTLinux for the PowerPC. \* The MULTI 2000 Software Development Environment from Green Hills Software is now available for the ARM processor family. \* U S Software's TronTask! real-time operating system now supports Intel's StrongARM processor. \* emWare has partnered with Invensys Network Systems. Motorola Semiconductor **Products Sector, GE Appliances,** and Sunbeam to produce end-toend solutions for networked devices. \* PointBase will bundle its 100% Pure Java database with Symantec's VisualCafe Development Environment. \* The Embed The Internet (ETI) Alliance has changed its name to the Extend the Internet (ETI) Alliance.

STMicroelectronics recently joined the group. \* Enea Data AB has acquired TekSci, a software consulting firm. \* NEC has entered into a licensing agreement with Tensilica for its Xtensa processor technology. \* The SC Series controller chip from Scenix Semiconductor is used in the Sennheiser Digital 1000 Series Wireless Microphone System's microphone and receiver unit. \* VMIC's generic device driver supports the QNX operating system. \* ESS Technology will use Green Hills Software's optimizing C compiler in developing embedded software for its Internet television settop box platforms. \* Radstone **Technology** and **Lynx Real-Time** Systems have partnered to provide Lynx's BlueCat Linux OS on Radstone's PPCx family of PowerPCbased SBCs. \* Netstream's OpenSSL will be ported to Enea OSE Systems' OSE RTOS. \* LinuxDevices.com has launched the Embedded Linux Polls center. The online polls track user and developer trends and preferences.

### VME Continues to Dominate Embedded **Merchant Computer Board Shipments**

The world market for merchant computer boards totaled \$1.98 billion in 1998 and is expected to total \$2.19 billion for 1999, according to a report by the Electronics Market Forecasters Group (EMF).

In 1998, VME shipments accounted for 53.2% of worldwide shipments, PCI accounted for 18.5% of shipments, and CompactPCI accounted for 2.2% of total worldwide board shipments. Combined shipments of ISA, EISA, Multibus, STD, PC/104, and S-bus constituted 16.0% of worldwide ship-

In 1999, VME shipments declined to 61.9% of worldwide shipments, notwithstanding an 8.5% increase in total revenues. PCI shipments accounted for 20.3% of worldwide shipments, whereas CompactPCI accounted for 3.6% of worldwide shipments.

Combined ISA, EISA, Multibus, PC/104, and STD shipments accounted for 14.2% of worldwise shipments in 1999 as ISA and EISA legacy sales continued their decline.

### NAMES IN THE NEWS

American Microsystems Inc. (AMI) has appointed H. GENE PATTERSON president and CEO. S. CAINE O'BRIEN has been promoted to CEO of ARTISAN Software tools. He was previously vice president of marketing and executive vice president of its North American operations. LARY EVANS has been named to Applied Microsystems Corp.'s (AMC) board of directors. Evans retired from Dell Computer Corp. in 1998, where he served as vice president and general manager of Dell's server business. Red Hat named MICHAEL TIEMANN chief technology officer. Aisys Inc. has appointed ORI INTRATOR vice president of sales and marketing for Europe and ELAN ROTH vice president of business development. ROBERT MOORE has been named vice president of marketing for CoWare. MEC Electronics Inc. has announced several management appointments: GEORGE WANG has assumed responsibilities to include general manager of the VR Series Microprocessor Strategic Business Unit. Wang will also continue his role as general manager for the consumer and automotive divisions; KARL AUKER was promoted to assistant general manager for the VR Series Microprocessor; CHUNG HO was appointed assistant general manager of the Communications Division; and STEPHEN TANG-KONG was promoted to associate general manager of Mixed Signal Technology Group.

BASEBAND PROCESSORS

GaAs-RF/IF-SOFTWARE

CMotorola, Inc. 1999, All rights recommended in Motorola, Inc. 1999, All

# Attention wireless designers: The candy store is now open.

THE HEART OF SMART.™

It's enough to make you drool. Open access to one of the broadest and deepest portfolios in the business. And it's everything you need to make your next mobile wireless solution work smarter. We call it DigitalDNA technology from Motorola: chips, systems, software and the ideas of thousands of innovative engineers who get just as excited about smart portable products as you do. You'll find DigitalDNA in wireless solutions like the first 1.8V dual-core baseband processor for digital cellular applications. The first IC to integrate two complete power amplifier chains for dual-band/dual-mode TDMA phones in a single chip. And the MPU used in the top-selling PDA in the world. We're ready to help your smart wireless device hit that proverbial sweet spot. www.digitaldna.motorola.com

DSP . DRAGONBALL" . RF/IF . MCORE" . POWER MANAGEMENT ICS

INFINEON CYCLES

HAS DESIGNING your 8-bit application and time-to-money pressures got you stressed out? Relax. Now working on 8-bit microcontroller applications couldn't be easier. Why? Infineon's broad C500 family has got all you need to stay cool. Each member is naturally 8051 compatible and features a versatile set of powerful peripherals with enhanced functionality. Plus they're very, very attractively priced. Looking for CAN, Motor Control, USB and OTP solutions? No problem. Need support? You won't after you've checked out our comprehensive set of development and support tools. And DAVE, our digital application virtual engineer, is always there to help. After all, we should know what design engineers want. We're Infineon – the people who never stop thinking of easy ways to get you through the entire design cycle.

www.infineon.com

complete solutions

We are there to help

Jack W. Crenshaw

# A Simulator's Paradise

After I finished and submitted last month's column ("And Another Thing...!" March 2000, p. 15), in which I released some of my pent-up frustrations about software that doesn't work, I realized that I hadn't kept my part of our bargain. When I originally announced my intention to tell you about software products to watch out for, I promised that the knife would cut both ways; I'd also tell you about the "good guys," companies that make good stuff, and are a pleasure to deal with. So before we get into the meat of this month's column, I want to try to even up the balance sheet a bit.

I've already told you about Matlab (see www.mathworks.com), which I've turned to as my baseline problem solver. No one who has attended college in a technical discipline, in the last decade, needs to be told about Matlab. It's become as ubiquitous on the college campus as Unix once was.

The biggest surprise about Matlab for me was that wonderful accessory called Simulink. In case you missed the description, Simulink is a "partner" program that runs on top of Matlab, and gives a GUI interface for building dynamic simulations.

You can take this to the bank: in my opinion, Simulink is the hottest thing to hit scientific computing since Fortran.

Unless you're old enough to be able to remember the "good old days" of Project Apollo and similar programs, you will have difficulty appreciating just how important simulation programs were, and have since become. I'm talking about simulations of dynamic systems, which can include

anything that moves, such as cars or spacecraft, but also anything that changes with time, like chemical reactions or populations of rabbits and foxes.

If you want to know how a car will work, or how rabbit populations will change, you can always build the car or breed the rabbits to find out. But if you want to know how to get to the Moon and back, you'd danged well

next: a multi-person, multi-year project fraught with massive cost and schedule overruns and a horrendous debugging/validation process. For years after I'd learned how to write good simulations in a short time, my biggest hurdle was convincing managers that I could really do what I said I could do, without the kinds of costs and overruns to which they had become accustomed.

# This month, Jack gets back to some Good Guys, his childhood (and adult) dreams of building legions of robots, and minima.

better be pretty sure you can do it, before you light that skyrocket.

My first simulation was one for a solid-fuel space booster. It was written in assembly language for an IBM mainframe, because Fortran hadn't yet been invented. My second, a simulation of Apollo, was written in what would now be called Fortran I, except we didn't call it that, because we never thought there would be a Fortran II.

Needless to say, those early simulations were crude; they took a long time to write. We were learning as we went, and the algorithms for things like numerical integration weren't well known. In years to follow, we got better at writing them.

Even so, for many years the words "computer simulation" were enough to make even the toughest managers blanch and feel faint. From experience, they knew what was coming

To paraphrase a book on Simulink I recently read, even as recently as 10 years ago, if you wanted to simulate a dynamic system, you really had no choice but to write a simulation from scratch. To be sure, we eventually got better at writing them, and we got software components that helped, but virtually every new simulation was a custom job, from start to finish, and it took time. Lots of time. And even after the program was completed, there was always the problem of demonstrating that the methods you used were really accurate enough to give meaningful results. In other words, you had to validate—a decidedly nontrivial exercise.

Nowadays, with a tool like Simulink, the problem has become almost trivial. In the olden days, we used to begin a new simulation by drawing out the design as a control system flow chart. We'd have boxes for

For years, I've dreamed of building and playing with robots of one sort or another. As early as age 12, I literally dreamed that I had built a robot of the C3PO class that would obey my every command.

the various components and lines connecting them to show how data flowed between boxes. That control diagram became the guiding light, the master plan for how the simulation program would behave.

With Simulink, the diagram is the program. Using a GUI interface, you drag boxes into a worksheet and connect them as needed. When you have the diagram drawn, you click "start" and your results are ready. It's as simple as that. The GUI interface of Simulink makes Visual BASIC look like assembly language. There is no programming to do at all. When the diagram is done, so is the simulation.

I can't begin to tell you how the availability of such a tool can change the way things get done. Just the other day, some colleagues and I were concerned with whether or not adding a new component to a dynamic system—a component that would tend to couple previously independent control loops-would destabilize the system. In the old days, to answer such a question would have involved either a complex simulation program, or a long and complicated stability analysis.

Using Simulink, I sat down and did a simplified version of the existing system. Then I added the new component. In a matter of about 20 minutes. we discovered two things:

- The new component did indeed destabilize the system

- We found a simple change that stabilized it again

The time saved in having a tool like this is, to me, incalculable. It means we are now free to concentrate on other things, such as having bright ideas, instead of slogging around inside variable-step Runge-Kutta integrators. It's

Did I mention that Simulink is revolutionizing the business of developing systems? I thought so. I know of at least two companies—companies who provide embedded systems to federal agencies—who have virtually stopped using either Fortran or C. They develop their systems and simulate them in Simulink. When they're done with their simulation, they use another Matlab tool, Real-Time Workshop, and generate the embedded code directly from the simulation. The engineers design and maintain the entire safety-critical and highly controlled software for the system, using Simulink alone.

If there's one problem with Matlab and its friends, it's the cost. Matlab is great, but it is not cheap. It should come as no surprise, then, that other companies have begun offering Matlab companions or Matlab equivalents, at lower cost. One that's come to my attention recently is Mathtools (www.mathtools.com), makers Mideva and quite a number of other products. I won't say much more about them now because I'm planning a review for the near future, but on the face of it the products look great, and I've heard very good things about them.

### **Fun and games**

"All work and no play makes Jack a dull boy," and I certainly have no desire to be dull. For years, I've dreamed of building and playing with robots of one sort or another. As early as age 12, I literally dreamed that I had built a robot of the C3PO class that would obey my every command. Using my trusty Gilbert Erector Set, I proceeded to try to build what I'd

dreamed of. Sadly, I learned that my engineering skills and Gilbert's technology weren't quite up to the challenge, and the reality fell considerably short of the dream.

Nevertheless, that dream keeps popping up in one guise or another over the years. It's one of the reasons I continue to tinker around with electric motors, pneumatic systems, and controllers. When Heathkit came out with their ill-fated HERO 1 robot, I thought I'd found the answer to my dreams, but that one just didn't quite make the grade.

Fortunately for me, the dream is slipping ever closer to reality. A few years ago, I discovered a wonderful company that was, apparently, a secret to no one but me. FischerTechnik is the modern, German equivalent of Gilbert, and they manufacture the European equivalent of the old Gilbert Erector Set. You don't hear much about FischerTechnik in the States, for the simple reason that they don't see much reason to do aggressive marketing here. They're already producing at top speed to meet the demands of the European market alone.

FischerTechnik makes a whole range of kits, mostly for kids, but they also sell some robotics kits that are intended mostly for the educational trade (many universities use them to train budding industrial automation engineers). Like Matlab, they are not cheap—my first three kits cost \$700, \$500, and \$500, and that was in 1990 dollars. But you will not believe the quality, which follows the traditions of German engineering. Beautiful, extruded aluminum beams replace the stamped-steel parts of the erector set. Self-stabilizing plastic connectors replace the old screws and square nuts. The electric motors are marvels of modern engineering-small, powerful, smooth, and quiet. Exquisite.

Most importantly to a budding roboticist, the FischerTechnik kits include controllers for both stepper and proportional motors, and a com-

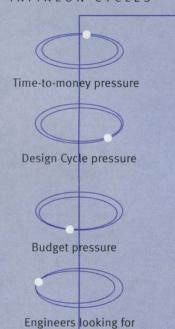

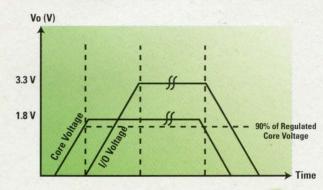

# DUAL-OUTPUT LDOS SIMPLIFY POWER-UP/POWER-DOWN SEQUENCING IN SPLIT-VOLTAGE DSP SYSTEMS.

20-pin TSSOP PowerPAD™ package

### POWERING A TMS320C5000™ DSP USING THE TPS70151

- Complete power solution from Texas Instruments for DSP, microprocessor, ASIC and FPGA applications

- Logic-selectable power-up sequencing prevents bus-contention possibilities

- Dual low-voltage outputs with fixed options for DSP core and I/O voltages

- > 250-mA/500-mA output current

- Integrated processor reset (SVS) with 120-msec delay

- 190-μA typical quiescent current ensures longer battery life

- TI's TPS701xx from only \$2.47 per device in quantities of 1,000

Sequential power-up and power-down showing core supply enabling and disabling I/O supply.

To order a free data book or LDO product catalog, call 1-800-477-8924, ext. aap3772u

For data sheets, application notes, samples and EVM availability, visit www.ti.com/sc/tps701xx

Power Manageme

Free Power Management Products Data Book

TMS320C5000 and PowerPAD are trademarks of Texas Instruments

8983-01 © 2000 T

© 2000 Wind River Systems, Wind River, the Wind River logo, How Smart Things Think, ISI, DIAB SDS, Doctor Design and TakeFive Software are trademarks and registered trademarks of Wind River Systems, Inc.

There's a new force sweeping across the landscape, ushering in a new era of embedded capability. An era of operating systems and development tools that are balanced, strong and consistent, like nature itself. What's behind this? The merger of Wind River Systems and Integrated Systems, Inc., including DIAB SDS, Doctor Design and TakeFive Software. Separately, these companies were leading the way in software for smart devices. Together, they will offer unprecedented expertise, drawing from a vast pool of resources to craft targeted solutions for their clients. So behold the power, and put it to work for you. Call Wind River at 1-800-545-WIND today.

www.windriver.com

How smart things think

An Elemental Operating Systems Company Has Formed.

Roll Up Your Windows.

### An autonomous, programmable robot isn't enough for you? How about a whole swarm of them, operating in unison?

puter program to control them. The kits using proportional motors have optical encoders to give position feedback. Other kits use other methods, such as potentiometers.

Most recently, FischerTechnik has begun selling robotics kits intended more for the private consumer. They feature more plastic parts, fewer metal ones, but the famous FischerTechnik quality remains. Their latest addition is a kit that provides computer control for pneumatic systems; as far as I know, a first in that area.

Last Christmas, I treated myself to a whole gaggle of FischerTechnik kits, with more on the way. I can hardly wait!

### Leggo my Lego!

Speaking of robotics: remember Lego? You know, those crazy plastic blocks that would never stay together? Well, they still don't stay together very well, or at least the poorly built things don't (you have to use a little engineering, after all), but Lego may very well have the hottest thing going in terms of robotics. It's the Lego Mindstorms Robotic Invention System (RIS). The key component of this system is the "smart brick," an oversized Lego block called the RCX controller. I understand that the RCX was developed for Lego by a team of MIT wizards, and it shows. Inside is a microcomputer. Unlike the Fischer-Technik systems, which require cables back to your computer, the Lego RCX is battery powered and IR-programmable, which is another way of saying that the Lego robots have cut the umbilical cord. They can operate autonomously.

The standard RIS includes two touch sensors (also known as microswitches), two optical sensors, and two motors, but there's more. Like a Barbie doll, the basic kit is only the beginning. Lego will be happy to sell you more motors, more sensors of all kinds, and more controllers that can work with the RSX. Lego robots can even—get this—communicate with each other, through either IR transmitters and receivers, or short-range CB radio. An autonomous, programmable robot isn't enough for you? How about a whole swarm of them, operating in unison?

For anyone who's interested in embedded systems, as I presume you readers are, and especially those who wish they knew more about how to control physical sensors and actuators, I can't think of a more enjoyable way to learn than to tinker with these robots. Space prevents me from mentioning all the sources for such gems, but fortunately, I don't have to; I need only give you the right search keywords for your Internet browser. Try the terms "construction," "robot," and "kits" in various combinations. Also, look for products by FischerTechnik, Lego, and K'Nex (not robots, but still fun). As you do, you will discover one more facet of owning a Lego Mindstorms kit: Lego gives each buyer a free Web page to display pictures and plans for his/her inventions. You'll surely run across several such Web sites.

Enjoy. Learn by doing. If what you find there doesn't give you even a little hankering to buy your kid a Lego toy (strictly for his own amusement, of course), you are either already a robotics expert with your own lab, or you would make a great accountant.

### **Back to minima**

Now let's get back to the main problem at hand, searching for good ways to find the minimum of an arbitrary function. We've managed to go remarkably far without having to do much math at all, beyond computing new trial values of the function, and evaluating it at each step. That situation is about to change. The methods we'll be talking about next all require considerably more mathematical rigor than we've needed so far.

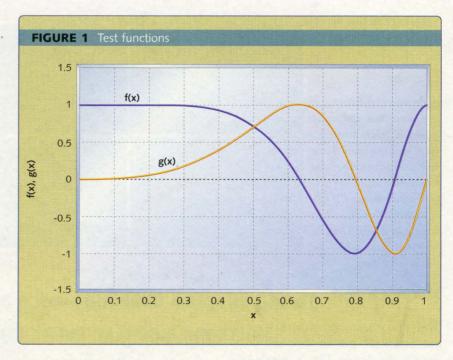

Since I haven't given our test function lately, and some of you readers have asked for it, here it is again:

$$f(x) = \cos(2\pi x^3) \tag{1}$$

The power of three in the function makes it just crazy enough, and also asymmetric enough, to keep it from being a trivial function. From elementary trigonometry, we know that f(x) has a minimum value of -1, and that minimum occurs when the argument is equal to  $\pi$ . So the value of x at the minimum is:

$$x_f = \sqrt[3]{\frac{1}{2}} = 0.7937005 \tag{2}$$

In the process of working up the code for last month's episode, I also settled on a second, very similar function:

$$g(x) = \sin(2\pi x^3) \tag{3}$$

Its minimum occurs when the argument is  $3\pi/2$ , which leads to:

$$x_g = \sqrt[3]{\frac{3}{4}} = 0.90856 \tag{4}$$

The two functions are plotted together in Figure 1. Each function has its advantages for testing. The function f(x) is well behaved in the sense that it has only one minimum, but it starts out very flat, which can cause trouble for some search methods. The function g(x) really has two minima, one of which occurs at x = 0. According to our originally stated criterion, which is that we will prefer the leftmost minimum, we should, by all rights, accept this value immediately. However, several readers have suggested that a good minimum-finder should be able to step along the func-

### "Imagination is more important than knowledge"

. . . Until you have to **build** what you've imagined.

### If You Need or Provide These Services:

- I concept

- I design

- I manufacturing

- I support / consulting

### Visit and Find:

- I product development RFPs

- I pre-qualified solution providers

- I emerging technology communities

- I imagination and knowledge morphing into reality

### Then it's time for

Web Product Realization Network.

Where Electronic Product Developers and Service / IP Providers connect to make ideas real. Faster.

Are you in or are you out?

The Fastest Way to Make Ideas Real.

### Much more than connecting buyers and sellers . . .

### For Product Development Companies:

- A more cost-effective and efficient sourcing process

- I Worldwide, pre-qualified expertise and resources

- I Supplier base expansion controls

- I Secure and anonymous RFP postings

- I Emerging technology communities

- I Reduced time to market

### For Service / Intellectual Property Providers:

- Reduced cost of sales

- Opportunities to win the *right* projects

- I High visibility to product development companies

- Access to potential symbiotic partners

- Millions in sales and marketing resources deployed on your behalf

- Emerging technology communities

And still there's more. Log in and learn. WebPRN.com

tion until it begins to have a negative slope (assuming that this ever happens), and ignore lower starting values. I thought their argument persuasive, and g(x) is the result. A robust minimum-finder should return the leftmost value if the function never turns south at all, and whatever minimum occurs after that, if it does. The routine I gave last month does do this.

### **Getting rigorous**

Both functions in Figure 1 share one common characteristic, which is that they are *differentiable*. In mathematical terms, this means that the function, and all its derivatives, are finite, no matter how high an order we choose to go. In layman's terms, the function is smooth, with no surprising discontinuities or other craziness. A key characteristic of such functions is that they can be expressed in terms of a Taylor series:

$$f(x) = f(x_0) + (x - x_0)f'(x_0) + \frac{1}{2!}(x - x_0)^2 f''(x_0) + \frac{1}{3!}(x - x_0)^3 f'''(x_0) + \dots$$

(5)

(where the primes imply the derivatives of successively higher orders, with respect to x). In words of few syllables, if we have f(x) at some value  $x_0$ , plus all its derivatives (a potentially infinite number), also evaluated at  $x_0$ , we can synthesize the function. Note that the series is exact, not an approximation, as long as we use all the non-zero derivatives of f(x). If the function happens to be a polynomial of some order N, the series will not be infinite, since all derivatives higher than Nth order will be zero.

The choice of the value  $x_0$  is arbitrary, though in practice we try to choose a value that's near the region of interest. That's because, also in practice, we tend to approximate the function by truncating the series.

You may recall my saying, in previous columns, that all well behaved functions look like parabolas when we look at a region sufficiently close to the minimum. Equation 5 gives us rigorous support to that assertion. Look at those coefficients for each term, which have the general form:

$$\frac{1}{n!}(x-x_0)^n\tag{6}$$

If we choose a value of  $x_0$  that's sufficiently close to the true minimum, and restrict our range of focus to a sufficiently narrow range, the value of  $x - x_0$  remains small. Its higher powers, then, are even smaller, and this smallness is greatly aided by the appearance of the n! term in the denominator. For these reasons, terms of order higher than two become negligible, and we can truncate the Taylor series to:

$$f(x) = f(x_0) + (x - x_0)f'(x_0) + \frac{1}{2!}(x - x_0)^2 f''(x_0)$$

(7)

This function doesn't just look like

a parabola; it *is* a parabola. Therefore our statement that all functions with minima look like parabolas is rigorously true if the function is differentiable and the magnitude of  $x - x_0$  is sufficiently small.

Now we can also give a rigorous definition for the location of the minimum, if one exists. The usual conditions are given as:

$$f'(x_{\min}) = 0$$

$f''(x_{\min}) > 0$  (8)

These two equations state mathematically what we know to be true, intuitively, for a mimimum. At the minimum, the slope is flat (that is, zero), and the function curves upwards in both directions as we leave the minimum. This statement is about as rigorous a definition of the minimum as you're likely to find. Oh, if you look hard enough, you can find a pathological function that has a true minimum, but the conditions of Equation 8 don't hold. For example, we can invent an "artificial" function such that not only the second derivative, but all higher

Having had this idea that functions look much like parabolas near their minima, it seems only natural to try to fit the data by assuming a parabolic shape.

derivatives through, say, the ninth, are zero, but the tenth derivative is positive. Such a function really does have a minimum. However, in practice nobody really cares, because the function would be so flat near the minimum that we'll never find it anyhow. For all practical purposes, if the function doesn't satisfy Equations 8, we'll throw up our hands and declare failure.

### How close is close?

We'll find it instructive to consider our test functions, and see how well they match the "looks like a parabola" description. The derivatives of these functions turn out to be:

$$f'(x) = -6\pi x^{2} \sin(2\pi x^{3}) = -6\pi x^{2} g(x)$$

$$f''(x) = -12\pi x \sin(2\pi x^{3}) - (6\pi x^{2})^{2} \cos(2\pi x^{3})$$

$$= -12\pi x g(x) - (6\pi x^{2})^{2} g(x)$$

(9)

Similarly,

$$g'(x) = 6\pi x^{2} \cos(2\pi x^{3}) = 6\pi x^{2} f(x)$$

$$g''(x) = 12\pi x \cos(2\pi x^{3}) - (6\pi x^{2})^{2} \sin(2\pi x^{3})$$

$$= 12\pi x f(x) - (6\pi x^{2})^{2} g(x)$$

(10)

Because f(x) and g(x) are related as cosine and sine, you probably won't need much convincing that g(x) = 0 when f(x) is at its minimum, and vice versa. One look at Figure 1 should help. Nevertheless, for the sake of rigor, we'll go ahead and evaluate the functions.

$$g\left(\sqrt[3]{\frac{1}{2}}\right) = \sin\left(2\pi\left(\sqrt[3]{\frac{1}{2}}\right)^3\right)$$

$$= \sin\left(2\pi\frac{1}{2}\right)$$

$$= \sin(\pi) = 0 \tag{11}$$

Similarly,

$$f\left(\frac{3}{\sqrt{\frac{1}{2}}}\right) = \cos\left(2\pi\left(\frac{3}{\sqrt{\frac{3}{4}}}\right)^{3}\right)$$

$$= \cos\left(2\pi\frac{3}{4}\right)$$

$$= \cos\left(\frac{3\pi}{2}\right) = 0$$

(12)

Thus Equations 9 and 10 become, at the minimum values of the function:

$$f'(x_f) = -6\pi x_f^2 g(x_f) = 0$$

$$f''(x_f) = -(6\pi x_f^2)^2 f(x_f) = (6\pi x_f^2)^2$$

(13)

$$g'(x_g) = 6\pi x^2 f(x_g) = 0$$

$$g''(x_g) = -(6\pi x_g^2)^2 g(x_g) = (6\pi x_g^2)^2$$

(14)

Substituting the values of  $x_f$  and  $x_g$  gives:

$$f''(x_f) = 141.0031837$$

$g''(x_g) = 242.1125289$  (15)

So our approximate functions are:

$$f(x) \approx -1 + 70.50159184(x - 0.793700526)^{2}$$

$$g(x) \approx -1 + 121.0562645(x - 0.908560296)^{2}$$

(16)

How accurate are these approximations? To find out, let's evaluate them at values of x that are fairly far from the true minima; far enough, say, to cause a difference of 5% in the full function range. That is, the function should be -0.9 instead of -1.0. My calculator says that the variations in x should be about 0.038 in f(x), and 0.029 in g(x). At these values (for f(x), a range of nearly 10% in x), the differences between the approximate and exact functions is on the order of 0.5% or less. Obviously, if we narrow the range of x down further, the range of error will also drop dramatically. Surely this justifies our assertion that, in the vicinity of the minimum, all differentiable functions look like parabolas.

### A little curve-fitting

Having had this idea that functions look much like parabolas near their minima, it seems only natural to try to fit the data by assuming a parabolic shape. Suppose we have three points, denoted by the ordered pairs:

$$P_0 = [x_0, y_0]$$

$$P_1 = [x_1, y_1]$$

$$P_2 = [x_2, y_2]$$

(17)

What we'd like to do is find the parabola that passes through them. We know that the equation of a parabola is a quadratic equation, with the general form,

$$F(x) = a + bx + cx^2 \tag{18}$$

Conceptually, we can require that this equation satisfy the constraints that:

$$F(x_0) = y_0$$

$F(x_1) = y_1$

$F(x_2) = y_2$  (19)

This gives us three equations to solve for the three unknowns a, b, and c.

You're welcome to try this approach, and you *will* get an answer, given enough perseverance. But you'll be doing a lot more work than is necessary. A better approach is to use Newton's form for the quadratic:

$$F(x) = a + (x - x_0)[b + c(x - x_1)]$$

(20)

The nice part about this form is that the entire x-dependent part vanishes when  $x = x_0$ , and the quadratic part vanishes at  $x = x_1$ . This makes it much easier to evaluate the coefficients. (Hint: file this little trick away for future reference. You will find that it saves you tons of work.)

Using this form, Equations 19 become:

INTEL CPU PLATFORMS WIDE AREA NETWORKING SYSTEM PLATFORMS DSP TECHNOLOGIES

HERE'S A NO-NONSENSE MESSAGE ABOUT OUR TOTAL TELECOM SOLUTION. DON'T BE FOOLED BY ITS SIMPLICITY.

### Only RadiSys offers the total telecommunications solution.

A solution this complete is hard to pull off. A lot of vendors offer different parts of telecom solutions. Only RadiSys has the vision and technical expertise to deliver the total, integrated solution across both PCI and CompactPCI architectures. RadiSys has acquired Texas Micro, and is now positioned to redefine how the market is buying OEM embedded telecommunications systems. Now you can let us put the total solution together. Download our comprehensive white paper on SS7, and find out how simple it is to get the total solution from one source at www.radisys.com, or call 1-877-837-6859.

State of the art Pentium, PII, PIII, IXP

Enterprise and carrier class CompactPCI and PCI system enclosures and backplanes

WIDE AREA NETWORKING Field-proven frame relay, SS7, ATM, T1/E1, X.25, IP and other protocols and interfaces

Advanced TI C6x voice processing solutions-hardware and algorithms

www.radisys.com/SS7

$$a = y_0$$

$$a + (x_1 - x_0)b = y_1$$

$$a + (x_2 - x_0)[b + (x_2 - x_1)c] = y_2$$

(21)

From the first equation, of course, we get the value of *a* directly. Substituting it into the second gives:

$$b = \frac{y_1 - y_0}{x_1 - x_0} \tag{22}$$

We'll find life a lot simpler here if we introduce the familiar  $\Delta$ -notation, also called the forward difference:

$$\Delta x_n = x_{n+1} - x_n \tag{23}$$

Then:

$$b = \frac{\Delta y_0}{\Delta x_0} = m_0 \tag{24}$$

which we recognize as simply the slope of the straight line between  $P_0$  and  $P_1$ .

The third of Equations 21 may now be written:

$$y_0 + (x_2 - x_0)[b + (x_2 - x_1)c] = y_2$$

or

$$c\Delta x_1 = \frac{y_2 - y_0}{x_2 - x_0} - \frac{\Delta y_0}{\Delta x_0}$$

(25)

At first glance, the terms like  $y_2 - y_0$  don't seem to fit very well into our difference operator scheme; but look again. We can always write:

$$y_2 - y_0 = y_2 - y_1 + y_1 - y_0$$

=  $\Delta y_0 + \Delta y_1$  (26)

and similarly for the x's. Thus:

$$c\Delta x_1 = \frac{\Delta y_0 + \Delta y_1}{\Delta x_0 + \Delta x_1} - \frac{\Delta y_0}{\Delta x_0}$$

With a little mathematical manipulation, we can write:

$$\begin{split} c\Delta \mathbf{x}_1 &= \frac{\left(\Delta y_0 + \Delta y_1\right) \Delta x_0 - \left(\Delta x_0 + \Delta x_1\right) \Delta y_0}{\left(\Delta x_0 + \Delta x_1\right) \Delta x_0} \\ &= \frac{\Delta x_0 \Delta y_1 - \Delta x_1 \Delta y_0}{\left(\Delta x_0 + \Delta x_1\right) \Delta x_0} \\ &= \frac{\Delta y_1 - \frac{\Delta x_1}{\Delta x_0} \Delta y_0}{\Delta x_0 + \Delta x_1} \end{split}$$

Then:

$$c = \frac{\frac{\Delta y_1}{\Delta x_1} - \frac{\Delta y_0}{\Delta x_0}}{\frac{\Delta x_0}{\Delta x_0} + \Delta x_1}$$

$$= \frac{m_1 - m_0}{x_2 - x_0}$$

(27)

This formulation gives us an easy way to generate the coefficients of the polynomial. Take the differences of successive *y*'s to get slopes (*m*'s), and the differences of successive slopes to get *c*. (Confession: if you didn't see this particular move coming, don't feel bad. I've been doing this kind of thing for over 40 years, and I just saw the trick a few months ago! Newton saw it a bit earlier.)

Okay, let's assume that we have the equation for the function-approximating parabola. How do we get the location of the assumed minimum? That's simple: we differentiate the equation, and require that the slope be zero. From Equation 20:

$$F'(x) = [b + c(x - x_1)] + (x - x_0)c$$

$$= b + c(2x - (x_1 + x_0)) = 0$$

Solving this for x, we get:

$$2x_{\min} - (x_1 + x_0) = \frac{-b}{c}$$

$$2x_{\min} = x_1 + x_0 - \frac{b}{c}$$

$$x_{\min} = \frac{1}{2} \left( x_1 + x_0 - \frac{b}{c} \right)$$

(28)

# SOFTWARE

### Listen to what our customers are saying...

"Thanks to you for your time and help.

I was able to rebuild my ROM this weekend and have everything ready for Monday" E. M.

"GREAT web site. Easy to navigate and lots of useful information." R. L.

"Get on the horn with Keil's support team...

it won't cost you a cent...They won't bite

your head off for asking questions."

M. C.

"The free evaluation CD, the toll-free technical support telephone number, and the availability of people to speak with were all key factors in our decision to purchase your products." D. C.

"This (support solution) was exactly what I needed! Thanks! :-)" R. S. N.

"We tried what you suggested. Now, it works. I really appreciate your efficient support!" X. J.

"I couldn't find our lab copy of the manual, so I used your (web) search engine to find the syntax for the directive. It was quicker than looking for the manual!!!!!" N. M.

'I LIKE my Keil tools..." B. N.

Compilers, Assemblers, Debuggers, and RTOS for the 8051, 166, and 251

C51 is the industry standard ANSI C compiler for the 8051. It supports all 8051 derivatives including the new USB & CAN devices

C166

C166 Version 4 is the easiest toolset to use for C16x code development. It seamlessly integrates with all C16x and ST10 emulators.

New compiler technology built into C251 is designed specifically for the 251 architecture. It takes full advantage of the new 16 and 32-bit registers and instructions.

### Call Today for a free CD-ROM.

Keil Software, Inc. 16990 Dallas Parkway, Suite 120

www.keil.com

Dallas, TX 75248-1903

Sales: 800-348-8051

972-735-8052 FAX: 972-735-8055

# WITH OUR CODE- AND PIN-COMPATIBLE DSPS, YOUR BEST WORK LIVES FOR GENERATIONS.

The ADSP-218x 16-bit DSP family. Fixed-point processing made easy.

The only thing more difficult than writing code is rewriting it—unless you're designing with 16-bit DSPs from Analog Devices. Our roadmap of over 250 code- and 100 pin-compatible

### Introducing the ADSP-2186M.

A 15-year tradition of compatibility. This newest family member offers:

- 75 MIPS for a \$4.95\* price per unit

- 100-lead LQFP and 10mm x 10mm mini-BGA packages

- 320 Kbits on-chip SRAM, with a pin-compatible roadmap to 2 Mbits

16-bit DSPs makes your design challenge easier. Start with the exact speed, power, and memory version you need from our popular ADSP-218x family. Complete your initial code faster using our simple algebraic syntax for assembly programming, and hardware features like zero overheading looping. Switch to a smaller memory size as the code matures, even if you are in production, without a hardware restart. Or offer multiple features and price points from a single

design. Whether you need the world's smallest DSP form factor, power consumption as low as .4mA/MIP, SRAM integration up to 2 Mbits, or high-performance data converters for easy integration, no one can provide you with more choices and design advantages than the DSP supplier with the unlikely name. Analog Devices.

For FREE samples, data sheets, and an evaluation board: Visit www.analog.com/16-bit or call 1-800-ANALOGD.

Before we just jump in and start writing code, we must tame the method to the point where we are 100% sure we can trust its conclusions, and even more importantly, we'll know when we cannot.

### What does it all mean?

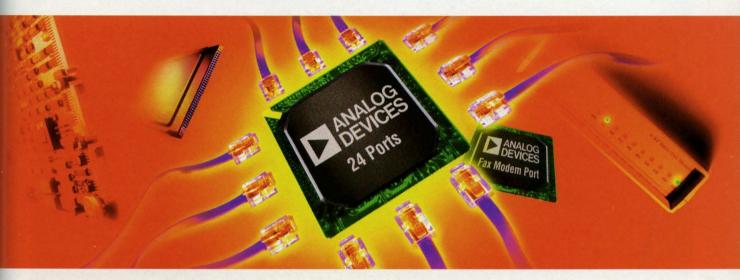

Now that we've done the math, what have we got exactly? What we have is a way to estimate the location of the minimum, given three points on the functional curve. We've already seen that most functions look like a parabola near the minimum, so our three points should give us a super estimate of the location of the true minimum. We have every right to expect that we should get much more rapid convergence than we would using a simple bisection algorithm. Do we actually get such rapid convergence? Let's find out.

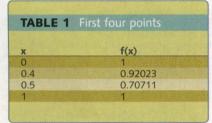

We'll begin with our standard test function, f(x), and bisect the interval to get a middle point lower than the other two (forget the Golden Section, at this point; it only complicates the math). We have, then:

$$\begin{array}{lll} x_0 = 0 & y_0 = 1 \\ x_1 = 0.5 & y_1 = 0.70711 \\ x_2 = 1 & y_2 = 1 \end{array}$$

$$m_0 = -0.5858$$

$m_1 = 0.5858$

$$c = 1.716$$

$x_{\min} = 0.5$

Oops! Houston, we have a problem: the algorithm says that the x-value of the minimum is the same as  $x_1$ , which means that, as far as it's concerned, we have already found the minimum. We know that's not true, but how are we going to tell the algorithm that it's wrong?

You can see that we will always get this kind of result, if the center point is obtained by bisection, and the values of f(x) at the other two points are equal. The algorithm will dutifully fit a parabola that's symmetric about  $x_1$ , and will steadfastly insist that it's found the minimum.

In retrospect, perhaps we would have been better off to use the Golden Section after all. At least we wouldn't have hit this crazy symmetric case. But, of course, there was method to my madness: I wanted you to see what kinds of problems we can encounter. It should be clear at this point that, while our method of fitting quadratics has the potential for greatly speeding up the search for the minimum, it is definitely not ready for prime time. Before we just jump in and start writing code, we must tame the method to the point where we are 100% sure we can trust its conclusions, and even more importantly, we'll know when we cannot. That process will take a little time.

Okay, so we're not quite ready to start committing the algorithm to code. Let's at least see what we can do by applying the method manually. We've seen that symmetric cases don't work, so we'll arbitrarily tweak the center point to a new value:

$$x_0 = 0$$

$y_0 = 1$

$x_1 = 0.4$   $y_1 = 0.9202$

$x_2 = 1$   $y_2 = 1$

$m_0 = -0.1994$   $m_1 = 0.1329$

$c = 0.3324$   $x_{\min} = 0.5$

Whoops! That didn't seem to help either. And you can easily see why. Think of the points  $P_0$  and  $P_2$  as the end points of a wooden bow, and the line between them as the bowstring. We can bend the bow up or down by choosing points that are left or right on f(x), and therefore higher or lower in the y-direction. No matter how we do this, however, we cannot warp the bow so that its minimum is at anywhere but x = 0.5. As long as  $y_0 = y_2$ , the parabola will be symmetric about this value.

At this point, it may seem that we've gotten nowhere at all. But don't despair: we've made more progress than you think. Let's tabulate the data we have so far. Table 1 doesn't give us

# Got another date with the old logic analyzer tonight?

TLA 600 — starting at \$7,000\* You keep looking, but you can't find the problem. Time for a state-of-the-art, affordable logic analyzer that provides 500 ps timing simultaneous with up to 200 MHz state on every channel through the same probe? And a Windows interface? That's detail, accuracy, and ease that'll get you home in time for dinner. For a free Solutions Brochure, call 800-426-2200 x3039 or visit www.tektronix.com/TLA600

much to go on, but, to quote Shakespeare's Tybalt in Romeo and Juliet, "T'is enough-t'will serve." In the last three entries, we have three points that satisfy our minimum-seeking criterion: the middle point is lower than the other two. That's all we need to start an iteration process.

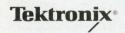

In Table 2, I've repeated the computations of Equations 24 through 27, manually choosing the lowest point and its two neighbors as the three points for the next iteration.

We can see two things from Table 2. First, the method definitely works. Including the first probing values of 0.4 and 0.5, we get the solution in only seven iterations, which is a lot fewer than the 20 or so we were needing using bisection.

In Figure 2, I've shown the parabolas fitted by the first few iterations. It's easy to see that the method has definitely gotten the scent of the true minimum, and is rapidly homing in on it.

The second thing we can learn

from Table 2 is that the method still needs a lot of work. Our first clue is the way the right-hand limit,  $x_9$ , seems stuck at 1.0 for so many iterations. Even when it comes unstuck, it seems to get stuck again at 0.79921.

Looked at in another way, during the time when the interval between  $x_0$ and  $x_1$  is reduced from 0.4 to 0.05, the overall interval from  $x_0$  to  $x_2$  remains stuck at about 0.264. This is not a good sign. One of the nice things about the bisection (also including the Golden Section search) methods was that we could count on the total interval being inexorably reduced during the search process. In fact, we used the width of this interval as our criterion to decide when we'd converged. As it stands now, the quadratic-fit method doesn't give us the same luxury.

A second problem is related to the first. In the last iteration, the distance between the points  $x_0$  and  $x_1$  is only 0.0016, which is only 20% of the total interval. I don't like the idea of any two of the three points getting too close together; it implies a risk of a poor parabolic fit because of roundoff error. I'd feel much more comfortable if we could make sure that both  $x_0$  and  $x_2$  are pulled in, in a roughly symmetrical manner.

What we have learned, then, is that while the method of fitting a parabola to the data is promising, we still have a lot of taming to do before it's ready for prime time as a robust minimum-finder. Since we were able to maintain a roughly symmetrical balance using bisection methods, it should come as no great surprise to you that the most robust methods are those that combine bisection and quadratic fit. That's the area that we'll concentrate on next month.

See you then.

Jack W. Crenshaw is a senior principal design engineer at Alliant Tech Systems Inc. in Clearwater, FL. He did much early work in the space program and has developed numerous analysis and real-time programs. He holds a PhD in physics from Auburn University. Crenshaw enjoys contact and can be reached via e-mail at jcrens@earthlink.net.

### You always believed there were more intelligent embedded tools out there.

You were right.

E-mail: c-tools@cosmic-us.com www.cosmic-software.com

Phone: US .......781 932-2556 France . . . . 33 1 4399 5390 UK ......44 01256 843400 Germany . . . 49 0711 4204062 Sweden . . . . 46 31704 3920

People doubted their existence yet you continued to search and now you've found them.

COSMIC C compilers are fast, efficient, reliable, and produce the tightest object code available. Cosmic Software's embedded development tools offer portability for a complete line of microcontrollers. All toolkits include IDEA, our intuitive IDE that provides everything you need in a single, seamless Windows framework.

Add ZAP, our non-intrusive sourcelevel debuggers and minimize your test cycle too. Want proof of their existence?

Download a free evaluation copy of our development tools at www.cosmic-software.com or call Cosmic today.

Cosmic supports the Motorola family of microcontrollers: 68HC05, 68HC08, 68HC11, 68HC12, 68HC16, 68300 and STMicroelectronics' ST7 Family.

# Royalty Free comprehensiv Productline Focus on Service All YOU NEED in an RTOS www.atinucleus.com

# There is only one conclusion.

Only one RTOS provides all the benefits you need. Accelerated Technology combines a level of service that is unmatched, an affordable pricing model and open source benefits with a vast, tightly integrated embedded product line offering.

Nucleus MNT - Windows-based rapid prototyping environment Nucleus EDE - intuitive embedded development environment based on Microsoft Developer Studio<sup>TM</sup>

Nucleus PLUS - robust, scalable, multitasking real-time kernel

Nucleus NET - complete TCP/IP networking protocol stack

Nucleus UDB - portable source level debugger

SurroundView and Nucleus ProView - revolutionary profiling tools that introduce a new level of application and OS monitoring

Nucleus WebServ - a tightly integrated, internet-enabling embedded web server

Nucleus WebBrowse - a compact and tightly integrated embedded web browser

Nucleus GRAFIX - portable embedded graphical user interface

These Nucleus embedded products support a wide range of processors:

- MCF5206, 5307

M-CORE

- PPC40x, 5xx, 60x, 7xx, 8xx, 82xx

- 680x0, 683xx

- ARM6/7/9, AEB, Atmel 40400, CL7110, 7111, 7209, Samsung SNDS100

- SA100-285, SA1100, SA1110

ARC

- SH1, SH2, SH3, SH4, SH3-DSP, H8S/2000, H8/300H

- IDT RC3081, RC4640/50, R5000, RC32364

- LSI LR 33000, 40xx, 410x, 64008, Lexra 4180, NEC 41xx, 4300, 5000, NKK 4650, Toshiba TX3904, 3927

- x86 RM/PM TriCore C167

For additional information on the complete Nucleus product line and how it can greatly diminish your timeto-market needs, royalty-free, please contact us at:

Phone: 1.800.468.6853

Address: 720 Oak Circle Dr. E. Mobile, AL 36609

Email: info@atinucleus.com Internet: www.atinucleus.com

All You Need in an RTOS. Royalty Free.

As the embedded systems development effort shifts more toward software and schedules begin to slip, project management becomes key to increasing productivity.

mbedded systems are by far the most prevalent of all computer systems used in the world today. More than 99% of all microprocessors sold in 1998 were used in embedded systems. Advances in processor and memory technology and their associated low cost allow them to be considered for an enormous number of applications. This, coupled with the expectations of customers, has led to tremendous growth in the size and sophistication of embedded applications.

Embedded systems share the following characteristics. They generally are developed around custom hardware, require high quality and reliability, and frequently deal with real-time issues. The applications running on these systems are usually very large and complex. Examples of these systems include telecommunication switching systems, aircraft, spacecraft, weapons systems, and the multitude of applications in the car and home.

Several trends are causing the driving factors in embedded systems development to shift from hardware to software. First, processors continue to push the performance envelope, allowing more flexibility in the applications which run on them. Second, functions are being increasingly integrated on the silicon. Functions which in the past required several devices can now be found on a single device. Many development organizations have found that they can simply purchase whole boards from manufacturers, thereby eliminating expensive and very long hardware design cycles. On some projects, software development costs comprise about 90% of the total development costs.

Most software projects fail to meet their schedules. A 1998 survey indicates that only about 24% of all software projects succeeded, up from 9% People represent the single largest factor in improving software productivity and quality. Issues include motivation, staffing, and teamwork.

in 1994. A 1997 survey indicated that 80% of all embedded software projects fail to come in on time. 2

In this article, I will present a number of techniques designed to improve the success rate of embedded projects. Three primary factors determine the success of a project: schedule, cost, and the quality of the delivered features. The ability of a company to optimize its project's schedule, cost, and quality objectives will give it a significant competitive advantage within its industry.

The development of software is one of the most complex activities ever undertaken. Despite significant advances in the methods and technologies for software development, it remains a people-oriented activity. As such, techniques that leverage the people and the way they develop software are the main factor in determining the success of a project.

I will focus on four areas of impact: people, process, product, and technology.<sup>3</sup> There are leverage points associated with each of these factors that are used to manage the risks to the success of a project.

### People

People represent the single largest factor in improving software productivity and quality. Issues include motivation, staffing, and teamwork. Steve McConnell summarizes the research concerning variations in productivity of individuals and teams:<sup>4</sup>

- Greater than 10-to-1 differences in productivity among individuals with different depths and breadths of experience

- 10-to-1 differences in productivity among individuals with the same levels of experience

- 5-to-1 differences in productivity

- among groups with different levels of experience

- 2.5-to-1 differences in productivity among groups with similar levels of experience

### Motivation

Most productivity studies have found that motivation is a stronger influence of productivity than any other contributing factor.<sup>5</sup> Hence, motivation can be your greatest ally on the road to a successful project.

We must now distinguish between motivation and movement as defined by Herzberg.<sup>6</sup> Motivation is a function of growth from getting intrinsic rewards out of interesting work. Movement is a function of fear of punishment or failure to get intrinsic

is focused on short-term results. Once the extrinsic reward disappears, so will the movement. Motivation, on the other hand, is based around personal growth being the ultimate reward. The benefit is long-term with no need of incremental extrinsic rewards.

Herzberg goes on to define the differences in motivating factors and hygiene factors. Motivating factors stimulate growth and performance. Examples of these include achievement, recognition, the work itself, responsibility, advancement, and growth. Hygiene factors represent the basic conditions a person needs to do his or her job. These include company policy and administration, supervision, interpersonal relationships, working conditions, salary, and securi-

| TABLE 1 | Comparison | of motivating | factors |

|---------|------------|---------------|---------|

|         |            |               |         |

|    | General population             | Software developers     | Software managers              |

|----|--------------------------------|-------------------------|--------------------------------|

| 1  | Achievement                    | Achievement             | Responsibility                 |

| 2  | Recognition                    | Growth                  | Achievement                    |

| 3  | Work itself                    | Work itself             | Work itself                    |

| 4  | Responsibility                 | Personal life           | Recognition                    |

| 5  | Advancement                    | Technical supervision   | Growth                         |

| 6  | Salary                         | Advancement             | Relationship with subordinates |

| 7  | Growth                         | Relationship with peers | Relationship with peers        |

| 8  | Relationship with supervisor   | Recognition             | Advancement                    |

| 9  | Relationship with peers        | Salary                  | Salary                         |

| 10 | Relationship with subordinates | Responsibility          | Relationship with supervisor   |

|    |                                |                         |                                |

Adapted from Boehm, Software Engineering Economics (1981) and Herzberg, "One more time: how do you motivate employees?" Harvard Business Review (1987).

rewards. Movement is the typical procedure used in animal training and its counterpart, behavioral modification techniques for humans. Examples of this abound in software companies as they strive to bring products to market in a competitive environment as quickly as possible. The behaviors that result from motivation and movement appear the same but have different long-term differences. Movement requires constant reinforcement and

ty. The conclusion to draw here is that the motivating factors are primary causes of satisfaction, and hygiene factors, at best, create no dissatisfaction. At worst, hygiene factors can create extreme dissatisfaction.

We can look at the motivating factors for software developers and their managers and come to some conclusions. While the data in Table 1 is a bit dated, it still offers significant insights. It should be clear that developers are motivated by a desire to be challenged and prefer an environment where they can grow in their positions. This represents an opportunity for the organization to allow the developers to stay current with trends in technology and methods. Note that developers are motivated by the work itself. An environment that allows them to focus on the work free of interruption is critical. This also suggests that a constant redirection of work will eventually cause problems between developers and managers. Developers are also motivated by their personal lives. Don't expect them to live their lives at work. Last, the data clearly shows that developers are usually not motivated to move into a management position. More often than not, promoting a developer to manager is a mistake and the organization will suffer.

### Staffing

Since software is developed by people, their selection for projects is of the utmost importance. Boehm presents five basic principles of software staffing.8 There is the principle of top talent. The idea here is to use better and fewer people. Given the productivity implications above, significant differences exist between good, average, and mediocre people. The best people will be much more productive. Therefore, fewer people will be needed. However, the most productive people will also cost more. It seems that management will consistently pick the person who costs less, but this ignores the data concerning productivity.

The second principle deals with job matching. The idea is to fit the tasks to the skills and motivation of the people. In terms of technical skills, larger projects have many areas of specialization. It's important to select people to fill these positions based on their areas of expertise. For instance, it would not be appropriate to place a person skilled in developing higher level application software in a position which would require the

development of embedded real-time firmware. The interpersonal skills of the people are also very important. Clearly, a person who is in a lead or managerial position needs to have effective communication and conflict resolution skills.

The third principle deals with career progression. An organization will benefit itself in the long run by helping its people to progress in their careers and keep current with the latest trends and technologies. It is also important not to force people to consistently work in areas where they are needed the most or have the most experience, but to let them explore other areas of interest. Of course, current business conditions will influence this activity significantly.

The fourth principle deals with team balance. The idea is to select people who will complement and harmonize with each other. The balance and coverage of a team are important considerations. Balance means that the team has a sufficiently diverse set of skills to achieve objectives. Coverage means that all critical skills needed are represented on the team. It is far better to have a team of average but solid performers dedicated to achieving results than it is to have one staffed with superstar developers engaged in adversarial relationships. The first team will easily outperform the second.

The fifth principle deals with phaseout: keeping a misfit on the team does not benefit anyone. Sometimes it becomes evident that a team member is not performing up to standards or is preventing everyone else from being productive. Perhaps the person is better as an individual contributor or would be better off leaving the team. The correct decision is to immediately deal with the problem and remove the person if necessary. In reality, this is more difficult than it seems. However, if the situation is allowed to languish, all team members will be affected, resulting in more problems than before.

### Teamwork

As software continues to become more complex, teams are increasingly the mechanism that determines the success of a project. Only teams can deliver the productivity enhancements needed to create complex software in a timely and cost-effective fashion. While much work has been accomplished in enhancing individual productivity over the last two decades, it is the productivity of teams that will be the deciding factor in the future.

Katzenbach and Smith define a team as "a small number of people with complementary skills who are committed to a common purpose, performance goals, and approach for which they hold themselves mutually accountable."9

Most teams usually consist of a small number of people, often between five and seven.10 Teams with less than five members risk not having the creativity needed, while those with more than seven can cause subgroups to form which increases the likelihood of conflict. Larger groups of people can form teams, provided each individual makes a significant commitment.

An effective team must have the right mix of skills. The first of these is technical or functional expertise. It is important that the team not be staffed by people of only one particular skill set. Problem solving and decision skills are also important so that team members can readily evaluate opportunities and problems and come to conclusions on how to proceed. Last, interpersonal skills are essential to group communication and resolving conflicts in constructive manners. A surprising conclusion here is that the team members do not need to have all of these skills at the beginning. The most effective teams quickly identify the gaps in skills and the specific training members need to acquire them. Individual accountability will promote the necessary learning.

A team's purpose and performance goals cannot be separated. A demanding performance challenge is an

## Pentium® Debug: \$4,995

Prototyping

environment

(VAD-P™)

### **RTXC™**

Royalty-free real-time OS

- TCP-IP stack

- File system

- Graphic system

### BeaconSuite™

- Compilers

- Linkers & Locators

- Debuggers

- Simulators

FINAL CODE

# Sometimes the shortest distance between two points covers new ground.

Embedded Power's Q.E.D. tradition continues!

We bring you accurate, dependable hardware-assisted source-level debug on the Windows® NT/95/98 platforms.

Using our own VisualProbe™ or other debuggers, Q.E.D. Jtag provides:

- Kernel-aware debug with our RTXC RTOS

- · Debug for all Pentium family members

- · Full visibility of all CPU registers

- Support for your favorite toolchains, including CAD-UL, Borland, MetaWare® and Microsoft®

- Fast, efficient host communications. High throughput means fast debug functions and quick code downloads even to FLASH.

- Requires NO fumbling with PC bus cards!

Standard connection to your PC is via an IEEE 1284/EPP parallel port.

- Eliminates the need to CAD a JTAG port to your board. We offer a complete set of JTAG breakout adapters that make hardware connection a snap!

Stay on course through Pentium-class embedded development with Q.E.D. Jtag Debugger!

www.embeddedpower.com

Pentium ITAG Port Pinout Breakout Board Processors PGA 320 Pentium I PGA 370/SLOT I Pentium II 30 Mobile Pentium II 30 **BGA/Micro BGA** Intel breakout board Pentium II Xeon 30 PGA 370/SLOT I 30 PGA 370/SLOT I Celeron

U.S. 281-561-9990 email: info@embeddedpower.com Europe: +44 (0) 1256 474448 email: eurosales@embeddedpower.com © 2000 Embedded Power Corporation Pentium® is a trademark of Intel Corporation

essential factor in team formation and must relate to the team's purpose or there will be confusion. Most teams get their mandate from management and it belongs to them both individually and collectively. An effective team is constantly shaping their purpose as this clarifies the implications to members. The purpose is translated into specific objectives, which keeps the focus on achieving results. The focus on results helps to push member status and personality issues away as well. Objectives also help the team to win the small battles that are essential to building commitment.

All team members must be committed to a common approach, a shared way of working together to accomplish their purpose. In order for this to happen, every team member must do equal amounts of real work and make substantial contributions. Members should agree on how this takes place; this helps to advance the team's performance objectives. There is also a need for social roles on a team, roles that provide support for members and keep everyone honest and headed in the right direction. These roles usually evolve of their own accord on effective teams.

For a team to exist, there must be mutual accountability. This means both individual and team accountability. Commitment and trust among team members helps accountability to flourish. Accountability tends to grow as the team's purpose, goals, and approach are developed. In many ways, the quality of the team's results are highly dependent on this joint accountability.

In discussing teams, it is important to look at various groups of people to determine how they fit into the team model. These small groups include working groups, pseudo-teams, potential teams, real teams, and high-performance teams:<sup>11</sup>

The working group is a group of people who are simply sharing information among themselves. There is

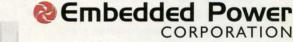

- no significant incremental performance need or opportunity that requires it to become a team